企业计算

台积电和Graphcore准备合作研发3nm AI加速芯片

在台积电的技术研讨会上,有一个侧面的消息是,台积电已经在客户研发3nm工艺节点技术。正如我们之前报道的那样,台积电正在开发其3nm,明年进行风险生产,2022年下半年进行大批量生产,所以此时台积电的主要合作伙伴已经在3nm PDK的初始版本上开发其未来的硅片。

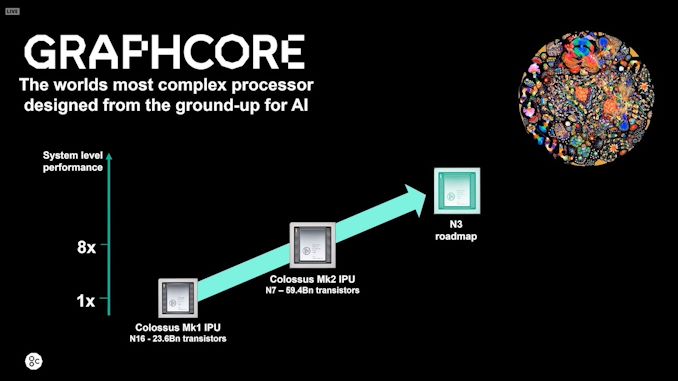

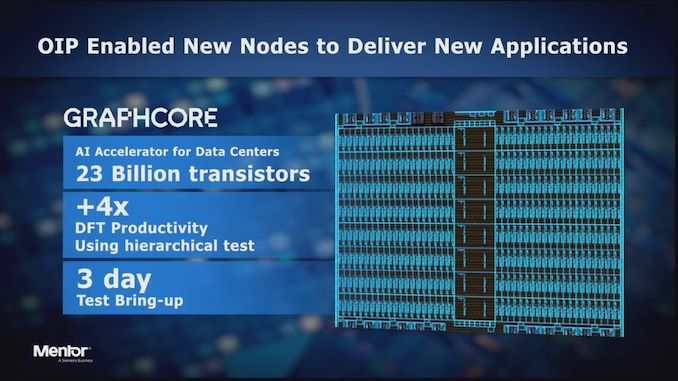

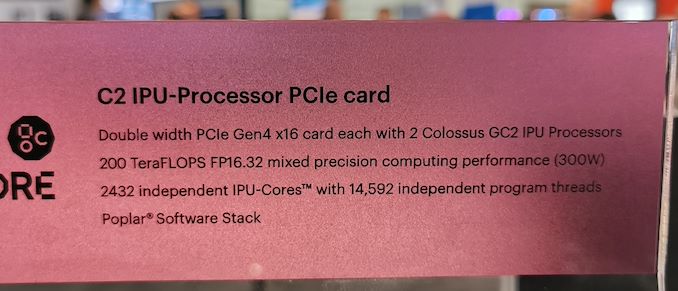

在台积电的演讲中,有一家公司被重点提及,那就是Graphcore。Graphcore是一家AI芯片公司,它制造的IPU,即 "智能处理单元",用于加速 "机器智能"。它最近发布了第二代Colossus Mk2 IPU,基于台积电的N7制造工艺打造,拥有592亿个晶体管。Mk2的有效核心数为1472个,可以运行约9000个线程,用于250 Teraflops的FP16 AI训练工作负载。该公司将4个这样的芯片放在一个1U中,可以实现1 Petaflop,还有450 GB的内存和IPU之间的定制低延迟结构设计。

根据台积电的介绍,Graphcore的未来一代产品,将以台积电3nm工艺为中心进行开发,跳过台积电的5nm。没有介绍具体的时间表,也没有说明Graphcore的策略。从幻灯片中我们可以看到,Colossus IPU产品线涉及大型高晶体管数量的芯片,使用更密集的工艺节点所提供的额外晶体管预算。

Graphcore首席执行官兼联合创始人Nigel Toon表示:"Graphcore是第一个打造出高晶体管数量芯片的公司。Graphcore率先建立一种全新的完全可编程处理器,从头开始为机器智能设计。我们的IPU架构的许多创新功能,以及即使在最新工艺节点的最前沿也能看到的高良率,都证明了我们与台积电的密切技术合作关系。我们在7月份发布的MK2 IPU拥有594亿个晶体管,并采用台积电最新的7纳米技术打造,是世界上最精密的处理器。每颗GC200 IPU拥有1472个独立的处理器核心和前所未有的900MB处理器内存储器,与MK1产品相比,实际性能提升了8倍。作为台积电的技术创新合作伙伴之一,我们将继续与台积电密切合作,探索包括N3在内的新工艺节点和技术的优势,以便我们能够继续提供更多的性能提升,使客户在人工智能领域取得新的突破。"

目前来看,Graphcore基于其Mk1和Mk2 IPU打造了多款产品,包括与戴尔合作的系统。2020年Q1的Graphcore在今年年初进行了D轮扩大融资,目前已经筹集了4.5亿美元,公司估值为19.5亿美元,投资者包括宝马、微软、DeepMind的CEO以及一些风险投资公司。据TechCrunch在2月份报道,该公司仍有3亿美元的现金储备。随着在最新制造节点上开发新硅片的成本增加,Graphcore在什么时候与台积电的3nm下单,或者台积电和Graphcore合作帮助优化大规模芯片的工艺,台积电是否会承担部分成本,目前尚不清楚。

本文由 Funstec非凡实验室 作者:Albert 发表,转载请注明来源!