行业动态

[推荐]3nm量产“意外”延期的背后 代工双雄在与时间赛跑

为争夺晶圆代工头把交椅的竞赛已趋白热化,台积电和三星都不惜撒下重金来获得工艺上的领先。但是,在双方全力争夺的3nm工艺节点开发上,近期却相继有开发遇阻的消息传来。在先进工艺已逼近物理极限之时,每进一步都要突破层层阻力。晶圆代工之间的争夺,不单是资金投入的比拼,还是与时间的一场赛跑。

与时间赛跑

苹果iPhone下一代的处理器无法采用台积电的3nm(N3)工艺了。这是台积电近期正式确认的消息,N3工艺的量产将会延迟3到4个月。而据相关媒体报道,三星的3nm开发也遇到了问题,其GAA工艺仍面临着漏电等关键技术问题。

按照之前的规划,台积电的3nm工艺将在2022年第三季度实现量产。3nm的具体量产时间是与客户共同协商决定的,台积电总裁魏哲家此前这样表示。苹果是台积电3nm工艺的首批客户,后有传闻英特尔也成为了尝鲜者,其GPU和服务器芯片将采用3nm工艺。不过,这一传闻在英特尔架构日上被破除,N5和N6将是台积电为其代工的首要工艺。

这一选择不能直接说明N3工艺的进展问题,但结合工艺进展延迟的消息,多少还是让人意外的。毕竟在4月15日的法说会上,台积电还表示N3已经提前至3月开始风险行试生产,并小量交货,进度优与原先预期。

局外人很难知道延迟的真正原因,可以看到的是工艺进展的不易。业界知名专家莫大康就表示:“从N5向N3不是单一的光刻尺寸的缩小,涉及器件架构、互连金属等,出现工艺延迟正常,要摸索工艺,需要通过更多的硅片生产来积累经验。”

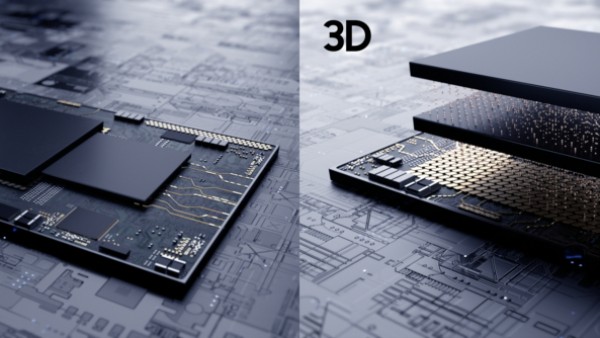

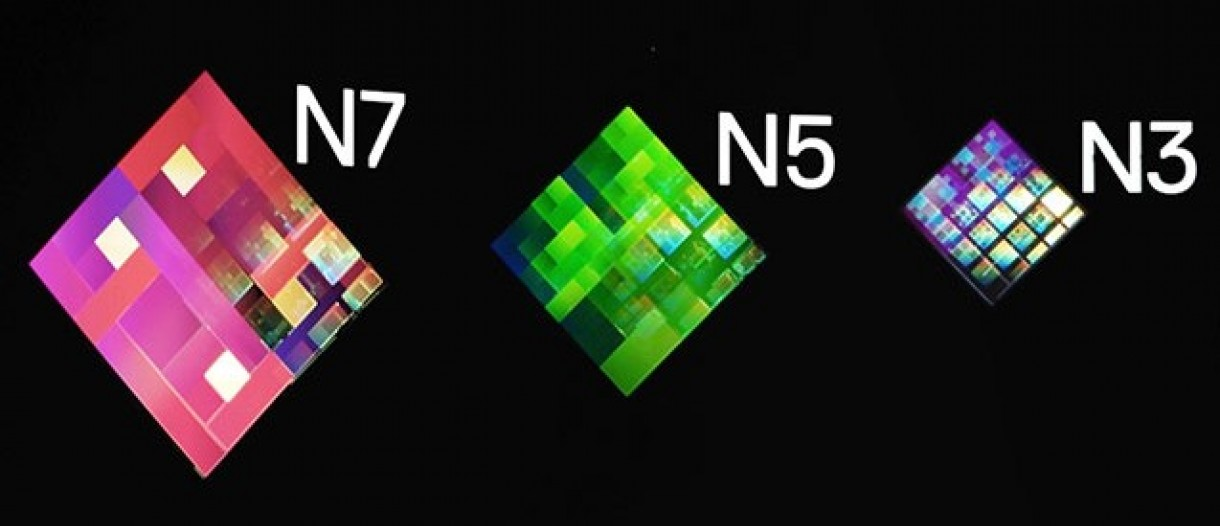

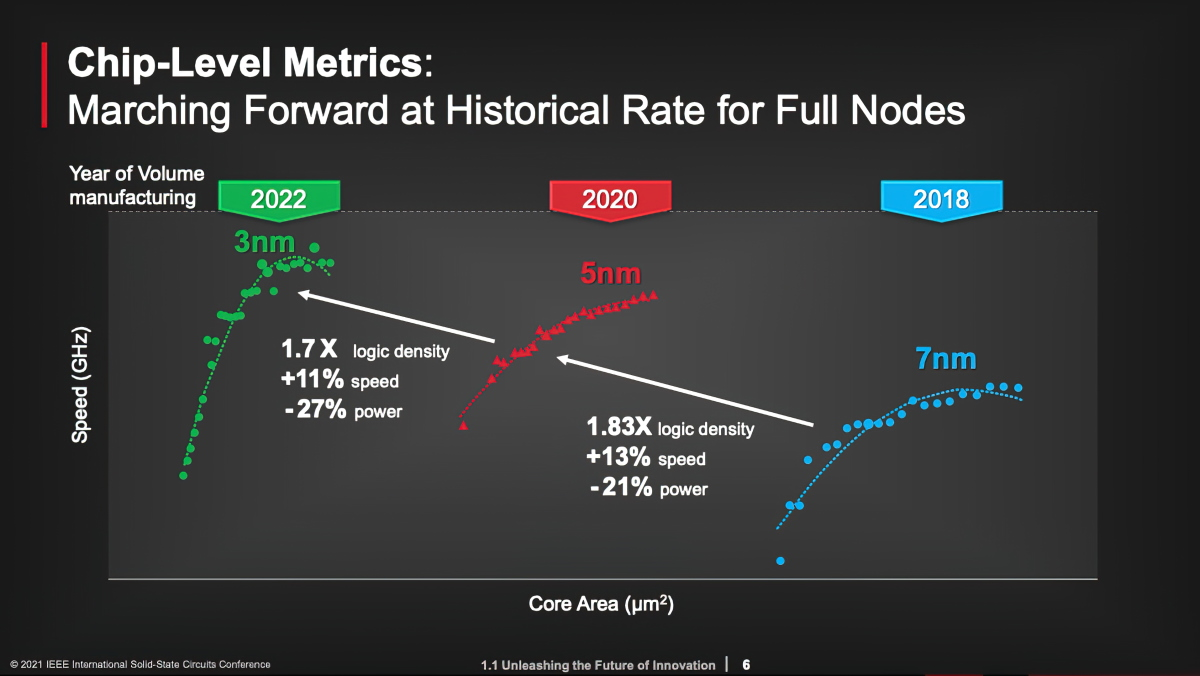

图 台积电的工艺进展

图 三星的工艺进展

不过一些英文媒体不看好三星能在2023年之前实现量产,依据就是疫情导致3nm工艺所需的极紫外光刻机(EUV)和其他关键生产设备的交付延期,进而推迟了量产的时间。

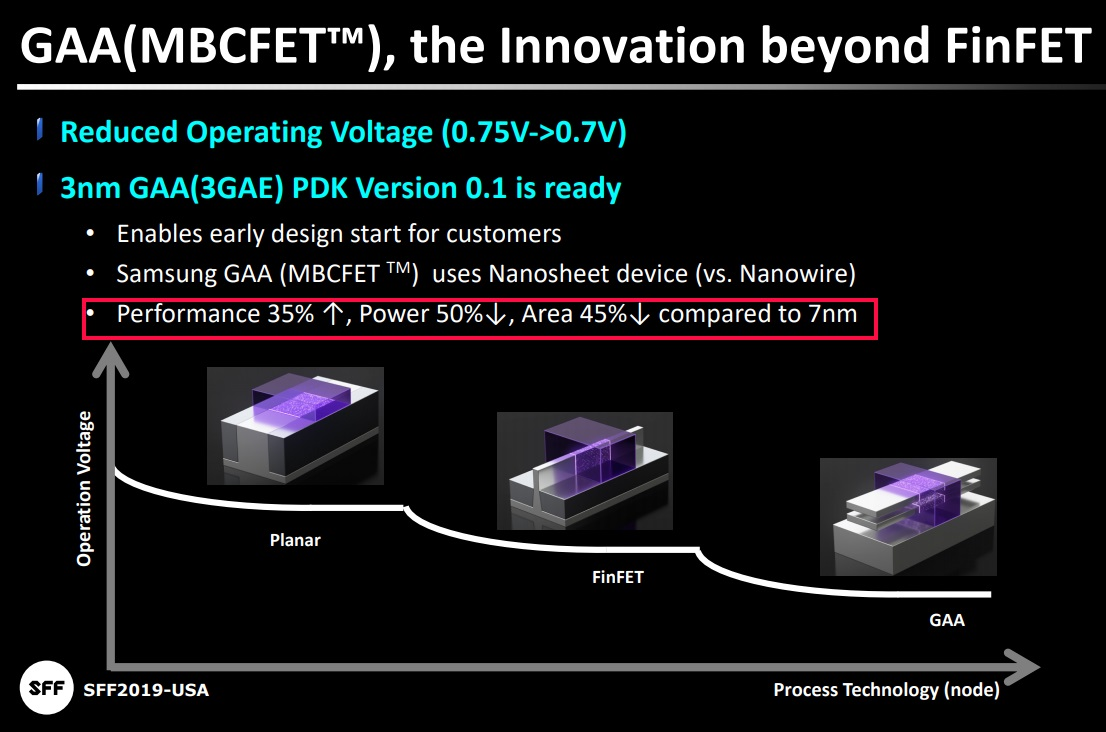

三星当初选择GAA工艺,就是因为想通过提前布局,在3nm节点实现弯道超车。三星的3nm GAA工艺分为 3GAAE / GAAP (3nm Gate- AlI-Around Early/Plus) 两个阶段,被业界认为真正成熟的将是GAAP工艺,GAAE将可能只是用于自己的芯片上。

与之相比,台积电继续在3nm节点选择FinFET工艺,则是考虑到可以继续挖掘现有工艺的优势,在三星之前实现量产。有业内人士就指出,台积电在GAA架构的开发上落后三星12至18个月,因而积极推进的3nm FinFET策略可以弥补这一劣势。

因此,三星的3nm工艺如果不能在2023年之前实现量产获得客户订单,那么将在代工领域处于不利地位。同理,台积电如果不能在时间上取得领先,也将面临被动的局面。

对于双方来说,都是一场与时间的赛跑。

要跨越技术鸿沟

3nm工艺的量产实现就像跨越鸿沟一样。就以光刻为例,晶圆代工厂希望尽可能地实现EUV单次曝光,因为这将可以简化工艺。然而,EUV单次曝光实现的间距极限是32nm到30nm 间,对应着5nm左右的工艺节点。要进展到3nm工艺,芯片制造商就要寻找新的方案。第一个选择就是EUV双曝光,第二选择是开发高数值孔径(NA)EUV 扫描仪,这是一个全新的系统。ASML的高数值孔径EUV系统采用新的0.55数值孔径透镜,分辨率提升了70%,仍在研发阶段。

高NA EUV系统复杂且昂贵,并且给晶圆厂中引入很多风险。此外,该系统不会为2022年的3nm初始阶段做好准备。根据最新的消息,这种新光刻机要在2025-2026年之间才能规模应用。因此,晶圆代工厂可能别无选择,只能采用EUV双曝光的方法。在双曝光方案中,芯片分割在两个掩模上并打印在晶圆上,既增加成本又会影响良率。

这还仅是开发3nm所面对的共同挑战,考虑到台积电和三星所采取的不同工艺路径,其各自都将面对不同的障碍。

台积电要将FinFET工艺从5nm迁移到3nm,就在理论上挑战了FinFET工艺的极限。在进入3nm之后,FinFET晶体管的鳍片难以在本身材料内部应力的作用下维持直立形态,尤其是在能量更高的EUV制程导入之后,这样的状况会更为严重。三星面临的困难也不少, GAA则是全新的架构,器件参数的不确定性会更大,很多影响将难以预估。

技术挑战之外,3nm工艺还将面对巨大的成本压力。IBS Research 2019 年的一份报告预测,虽然3nm芯片的每晶体管成本将降低,但晶圆和芯片模具的总体成本将增加。IBS在其研究中估计,10亿个晶体管部分的单个晶体管部分将达到2.16美元,低于5nm工艺的2.25美元。不过,3nm单片晶圆的成本为15,500美元,比5nm增加3,000美元,模具将比上一代的23.57美元高出30.45美元。此外,由于3nm预计将采用25层EUV光罩,因为代工价格将可能达到30,000美元。考虑到不是每个客户都能承受,因此台积电正评估启动持续改善计划(Coutinuous Improvement Plan),推出改款版3nm,通过减少EUV光罩层数、略增加芯片尺寸,降低成本、提高良率,提供客户兼具性能和成本的解决方案。

所以,3nm的开发也就成了一场金钱投入的竞赛。三星表示,到2030 年逻辑芯片投入将达1,077 亿美元。台积电也将资本支出以一调再调,由原来的250-280亿美元调整到300亿美元,其中80%将用于3nm、5nm等先进制程。

好在凭借多年形成的口碑,台积电的3nm没有量产却已经订单排满,苹果、AMD都先后预约了明后年的产能。按照台积电的说法,HPC的潜在客户和智能手机领域对N3的兴趣都很大。此前的规划中,3nm正式量产时的初期月产能为5.5万片,2023年月产能可达10.5万片。如果这些产能都被预定一空,台积电将在3nm代工市场再次拥有领先优势。

不过,三星的情况也稍显特殊。与专心做代工业务的台积电不同,三星是一个IDM公司,其总产能多为自己使用。2020年,三星将其晶圆代工厂产的60%用于内部使用,主要用于智能手机的Exynos芯片。其余产能来自非专属客户,高通占20%,其余20%来自Nvidia,IBM和英特尔。如果3nm工艺实现量产,靠其内部还是能消化很大一部分产能的。现在唯一要注意的就是不能再出现失误,拖延量产进度。

不过,3nm工艺进展表面是两强的竞争,实则是整个产业链的跟进。正如莫大康所指出,3nm是一个焦点,不能仅靠台积电、三星的推进,最终还要看制造商和设备商等产业链各个环节的努力。

本文由 Funstec非凡实验室 作者:Albert 发表,转载请注明来源!