行业动态

加速“摩尔定律”:通用芯片高速互连联盟致力推动“小芯片”设计

行业动态

4 年前

2.53W

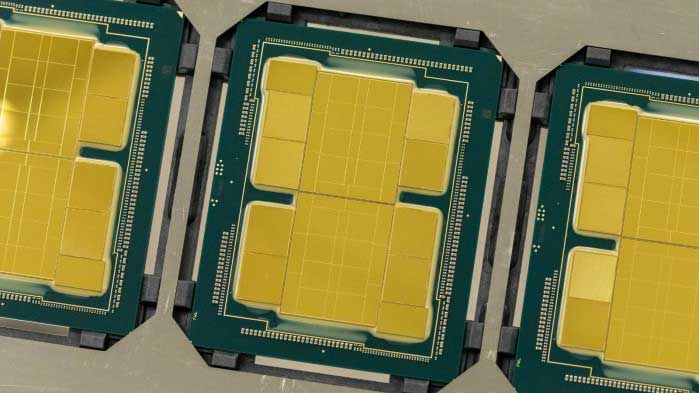

随着工艺制程的不断缩进,芯片制造商想要延续“摩尔定律”正变得愈加困难。为了继续提升晶体管密度和性能,各大厂商不约而同地选择了“小芯片”方案。以英特尔为例,其 Ponte Vecchio 项目就将多个“小芯片”封装到了一个庞大的处理器中。周三的时候,通用芯片互联高速联盟(UCIe)又宣布了让“摩尔定律”延续下去的最新计划。

Ponte Vecchio 处理器的晶体管总规模可超 1000 亿个

据悉,UCIe 联盟成员包括了芯片制造商英特尔、三星和台积电,以及芯片设计商 AMD、ARM、Google、Meta、微软、以及高通。

多年来,处理器一直由单独的矩形、带有电路的完整芯片组成。但随着规模的不断提升,厂商正在积极通过可重复使用的小元件来降低成本和提升封装效益。

虽然英伟达和苹果都未表态,但三星电子内存业务副总裁 Cheolmin Park 还是在一份声明中称:“我们希望 UCIe 联盟能够培育出一个充满活力的小芯片生态系统”。

UCIe 的工作,旨在标准化不同小芯片之间的通信链接。由于它们是从较大的晶圆(硅晶片)上切割出来的,理想状况下,这么做可显著降低 MCM 方案的障碍。

最后,随着“小芯片”封装技术逐渐扩展到更多主流设备(比如采用 3D V-Cache 堆叠缓存方案的新款 AMD 处理器),我们将不仅能够在 Aurora 这样的超级计算机上看到它的身影。

本文由 Funstec非凡实验室 作者:Albert 发表,转载请注明来源!