企业计算

[推荐]迈向摩尔定律的又一步:三星与台积电冲击5纳米制程

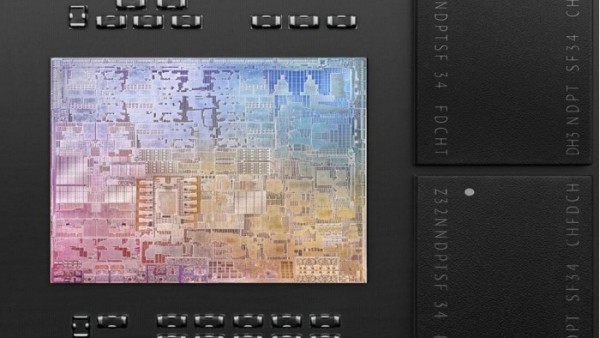

全球范围内规模最大的两家晶圆代工厂——台湾半导体制造企业台积电与三星公司,已经于今年4月宣布将再次冲击摩尔定律的极限。台积电方面首先发言,表示其5纳米制程工艺目前正处于“风险生产”阶段——具体来讲,该公司认为流程设计已经完成,但早期客户仍然对其适用性保留意见。三星公司随后迅速跟进了类似的声明。

台积电公司表示,其5纳米制程工艺能够实现15%的速度提升或者30%的能效提升。三星方面亦承诺借此带来10%的性能提升或者20%的能效提升。分析师指出,这些数据确实与预期相符。然而与十年前时常出现的高达50%的增长相比,如今的摩尔定律已经不再像过去那般“给力”。但从大型晶圆代工厂的投入来看,客户仍然认为这一切都物有所值。

为何5纳米值得大书特书?

5纳米节点是首个从起步阶段就采用极紫外光刻(简称EUV)进行制造的节点。EUV射线的波长仅为13.5纳米,可在硅片之上生成极为精细的图案。其中一部分图案虽然也可以使用上一代光刻工具完成,但却至少需要三到四轮光刻,才能在硅片上生成等同于一轮EUV光刻的结果。

性能与能效改进情况

来源:三星;台积电(与原有节点的原始版本比较)

各大晶圆代工厂此前在没有EUV的情况下进行过7纳米制程生产,但随后决定采用这一新技术减少光刻步骤量进而提高产能。而对于5纳米制程而言,代工厂在使用EUV的情况下一般只需要10到12轮光刻操作;但如果继续沿用旧有技术,那么可能需要30个甚至更多操作步骤。

由于包含这些图案的光掩模非常昂贵,因此每一台光刻机本身都代表着一项价值超过1亿美元的投资。VLSI Research的G. Dan Hutcheson表示,“EUV的每层成本更高。”但由于每块晶圆都将在EUV技术的帮助下带来更高净收入,因此EUV无疑将成为未来一切制程工艺的核心。

做出的产品卖给谁?

新的制程工艺显然并不适合所有人,至少目前还不适合。但两家公司都发现了一些可能的早期采用者,例如智能手机应用处理器与5G基础设施供应商。HIS Markit公司半导体制造分析师Len Jelinek所言,“要完成销售目标,厂商首先必须具备高产能,同时提供速度或者能效层面的提升。”

TIRIAS Research公司的Kevimn Krewell亦解释称,各大芯片制造商也在面临着巨大的压力。图形处理单元、现场可编程门阵列以及高性能微处理器曾经是摩尔定律的前沿探索主力。但随着这方面市场竞争空间的缩小,移动处理器必须利用新的技术为自己找到独特的发展途径。

未来的市场是否只剩下这两家公司?

目前只有台积电与三星公司能够提供5纳米晶圆代工服务。据分析师所言,GlobalFoundries止步于14纳米制程,而英特尔在推迟了几年之后,也只给出了相当于竞争对手7纳米制程水平的芯片产品。

三星与台积电之所以能够继续前行,是因为双方能够负担得起如此巨额的投资,并期望获得合理的回报。三星公司是2018年收入数字最为可观的芯片制造商,但其代工业务只在全球排名第四。台积电在这方面处于领先地位。台积电公司2018年的资本支出为100亿美元。三星预计到2030年才能在晶圆代工的年投资额度方面与台积电看齐。

如果真的只有两家厂商能够实现最先进的制造工艺,那这个行业还能继续正常发展吗?Hutcheson表示,“但这并不是能或者不能的问题。代工行业必须得正常发展。”

Jelinek指出,“只要我们至少还有两种可行的解决方案,那么整个行业基本上还是安全的。”

展望未来

从传统角度讲,芯片制造商在达成7纳米目标之后自然就会冲击5纳米,而后是3纳米。但分析师们表示,估计未来各代工厂商只能通过各类增量性技术以渐进方式填补空白。实际上,三星与台积电都在发布其所谓6纳米制程产品。代工厂需要这些蹭产品,以逐步帮助客户走向摩尔定律的真正极限。毕竟,5到0之间已经没有多少升级空间了。

本文由 Funstec非凡实验室 作者:Albert 发表,转载请注明来源!